This article is about arm microcontroller basics,introduction, architecture, versions, features and applications. ARM is short for “Advanced RISC Machines”. The ARM processor belongs to the family of CPUs which are based primarily on Reduced Instruction Set Computer (RISC). The ARM processors could be of 32 bit or 64 bit. The RISC processors are higher in speed because they perform a small number of instructions.

ARM microcontroller

The ARM processors have a less number of transistors because they have a reduced instruction set, which allows a smaller size for the IC. Thereby being space efficient also. Most of the electronic devices such as tablets, mobiles, smart phones and other mobile devices consist of these processors.By combining the ARM microprocessor with RAM, ROM and other peripherals in one single chip, we get an ARM microcontroller, for example, LPC2148.

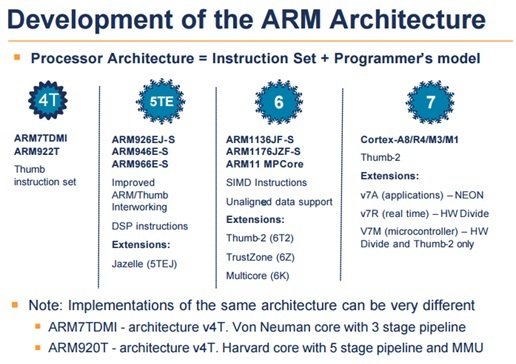

ARM ARCHITECTURES

A 32 bit RISC Load Store Architecture is present in ARM machines. The manipulation of memory is not possible directly; the registers are used for this purpose. Different varieties of operations are offered by the instruction set but the main focus is to reduce the number of cycle required for each instruction.

The instructions present in the ARM ISA are all conditional. The condition AL is accompanied by normal execution instructions. Excluding the condition AL, 14 other conditions are also available. The number of transistors has increased from 30000 in ARM2 to 26 million in the cortex-A9 ARM. A Thumb architecture was also developed which supported 16 bit instructions. Increasing the code density caused a drop in performance of these machines. But it was compensated by Thumb 2.

THUMB

The thumb mode has been featured by the processors from ARM7TDMI to help in improving the compiled code density. The 16 bit instructions are executed in this mode and they are mapped to the normal ARM instructions.

The opcodes that are smaller in size show less functionality in thumb. Some opcodes cannot access all the registers and only the braches can be opted as conditional. Smaller opcodes are more efficient.

Usually a very small amount of RAM is accessible with a datapath of 32 bit in embedded hardware. Rest of it is accessed by a 16 bit path. Therefore it becomes logical to use 16 bit thumb code and the wider instructions can be placed in a memory which is accessible by 32 bit. The ARM7TDI was the first process having a thumb instruction decoder.

DSP ENHANCEMENT INSTRUCTIONS

New instruction set was added to improve the architecture of ARM for multimedia applications and digital signal processing. These are specified by adding an E in the architecture’s name such as ARMv5TEJ and ARMv5TE etc. these are just the variations added on count leading zeros and saturated subtract and add operations etc.

JAZELLE

Besides the ARM and Thumb modes, a new technology has been introduced which allows the execution of Java bytecode in hardware. This technology is known as Jazelle. It is most prominently used in mobile phones so that the execution speed of Java EM games can be increased. The Java Virtual Machine performs the complicated operations in software while the Java bytecodes are usually run on hardware.

The first processor to use Jazelle was ARM926EJ-S and the architecture of ARMv5TEJ specifies the functionality of Jazelle. The JVM software depends on the details of hardware interface so that the JVM and hardware can develop very well together and no other software is affected.

THUMB-2

The Thumb-2 technology was introduced on ARM1156 core and it was announced in the year 2003. It increases the breadth of the instruction set by adding 32 bit instructions to the limited 16 bit instruction set of the previously mentioned technology Thumb. The code density resembling the Thumb is achieved by the Thumb-2 and also its performance is similar to the ARM instruction set on a memory of 32 bit.

The instruction set Thumb-2 is supported by all the ARMv7 chips. But some of the chips for example cortex-M3 only supports the Thumb-2 instruction set.

THUMB EXECUTION ENVIRONMENT (THUMBEE)

The ThumbEE first appeared in the Cortex-A8 processor. The instruction set is increased as compared to the Thumb-2 instruction set. Thumb EE is used for languages such as Python, Limbo, Java, C# and Perl etc. smaller codes are outputted by the JIT compilers and there is no significant impact on the performance.

ADVANCED SIMD (NEON):

The advanced SIMD (Single Instruction Multiple Data) also known as the NEON technology, is a combination of 128 bit and 64 bit SIMD instruction set. It provides acceleration for the applications of signal processing and media.

Its execution operations include decoding of MP3 audio on 10 MHz CPUs, and runs GSM AMR (adaptive multi rate) speech codec at 13 Mhz. it supports up to 64 bit integers and also handles games and graphics as well as audio/video processing. The SIMD in NEON can support 16 operations at a time.

VERSIONS AND FEATURES OF ARM MICROCONTROLLER

One of the most advanced form of these microcontrollers is the cortex microcontroller, developed by ARMv7. The cortex family is further divided as:

- Cortex Ax series

- Cortex Rx series

- Cortex Mx series

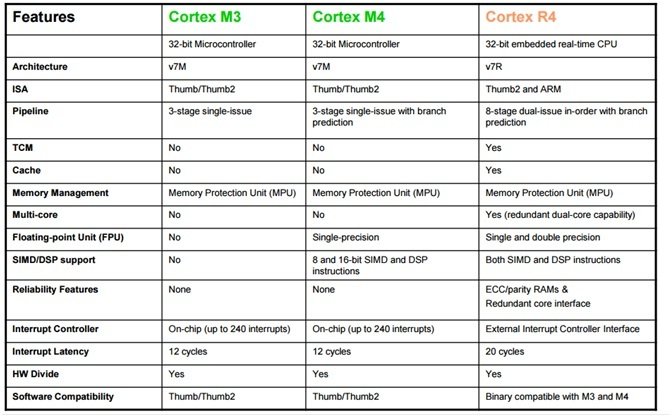

CORETEX M3 MICROCONTROLLER FEATURES

It is a 32 bit processor offering many advantages over other microcontrollers. It is a ‘harward architecture’. For communication with Ram and Rom, this architecture provides separate instruction buses and data buses. It consists of a 3 stage pipeline which fetches the instructions, then decodes it and then finally executes the instruction.

The memory required for the program has been reduced and also it provides high code density because of the usage of THUMB-2 technology in coretex-M3. For the good interrupt performance, the core m3 is closely integrated to NVIC (Nested Vector Interrupt Controller).

- It is a Reduced Instruction Set Computing (RISC) controller. It has a high performance CPU of 32 bits and the pipelining is done through 3 stages.

- The Thumb-2 technology has been integrated in these controllers, which means they can handle 16 bit as well as 32 bit instructions. This technology also provides high performance in operations and executions.

- It has low power modes. Sleep modes are also supported by it. It controls the software efficiently and it consists of multiple domains of power.

- The NVIC, Nested Vectored interrupt controller provides low latency as well as low jitter interrupts response. Another advantage is that there is no need of assembly programming in it.

COMPARISON BETWEEN DIFFERENT VERSIONS OF CORTEX

The features and specifications of cortex m3, cortex m4 and cortex R4 can be compared as in the following table:

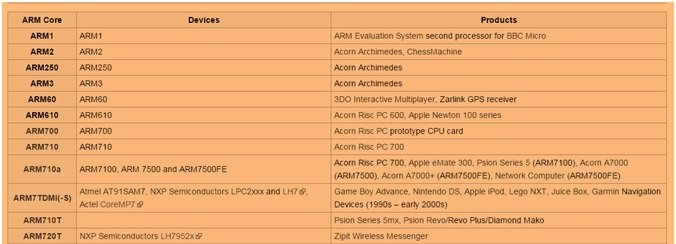

APPLICATIONS of ARM microcontrollers

Some of the applications of the cores of the ARM have been listed in the table below:

- Other than that the ARM microcontrollers can also be used in space and aerospace technologies.

- Used in many medical equipments such as MRI, CT scanner, ultrasound and implantable devices.

- Also used at the research level in particle accelerators, nuclear reactors and X-ray cargo scanning applications.

Photo Credit: