Every microcontroller out there contains a processor which is responsible for performing all the actions on that microcontroller. Each processor is designed, based on a certain instruction set Architecture architecture. That architecture can be based on any type, for instance, ARM. Being our topic of discussion today let’s explore ARM Cortex-M4 microcontrollers architecture in detail.

ARM Microcontroller Introduction

The abbreviation of ARM was later recognized as Acorn RISC Machines but with the time it has been upgraded to Advanced RISC Machines. The important point to discuss here is that ARM doesn’t develop microcontrollers silicon chip but it only provides IP core for a microprocessor and other building blocks of a microcontroller. ARM then provide it to the various manufacturer through licensing. The designs ARM provides are known as Intellectual Property (IP), and the business through which it sells the design is known as IP licensing.

ARM Cortex-M Microcontrollers Architecture

After enough discussion about ARM let’s move to the architecture designed by ARM name Cortex-M architecture. ARM Cortex-M architecture highly efficient, low cost and energy-efficient processor and it has been used in millions of customer devices. The reason for such diverse use of ARM Cortex-M profile is that its capabilities vary in a wide range from a vendor to vendor. It can be stated as “one microcontroller from one vendor using ARM Cortex-M will vary from other microcontrollers from a different vendor in hundreds of capabilities”. This flexibility is the main reason why these cores are widely used by hundreds of vendors to support additional features in a single microcontroller board.

ARMv7

As every manufactured device, ARM also have various versions and these versions keep on upgrading with time. Cortex-M belongs to the version of ARM names, ARMv7. Before this these were ARM versions named as ARMv4, ARMv5, ARMv6, and them comes ARMv7. Along with Cortex-M there are 2 other cores present in this architecture of ARM.

Cortex-M: Processors in these profiles are used for the development of microcontrollers based embedded systems. The Cortex-M family consists of Cortex-M0, Cortex-M0+, Cortex-M1, Cortex-M3, Cortex-M4 and Cortex-M7.

Cortex-A: Processors in this profile are used in high performance application devices like mobile/cellular phones.

Cortex-R: Main market of processors of this profile are in the real time application, where less response time is the main target.

ARM Cortex-M4 Introduction

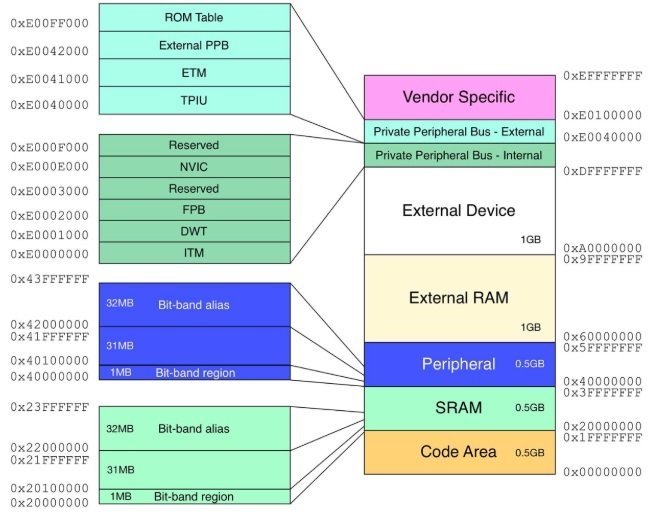

ARM Cortex-M processors are used in microcontrollers family of ARM microcontrollers. It consists of 32-bit processor cores. The size of processor in terms of bits defines the maximum addressable range or the maximum address range it can handle. For example, ARM Cortex-M4 microcontrollers can handle 2^32 = 4GB of memory address space.

For further information on Cortex-M4 memory address and memory mapped peripherals, read the following article:

The 32-bit also means the size of internal registers of the processor. All internal registers such as general purpose and special function, are of 32-bit. Moreover, datapaths, functional units ( ALU) which perform arithmetic (addition, subtraction, multiplication, etc) and logical operations ( AND, OR, less than, greater than, etc) on data are also of 32-bit size. Bus interfaces such as memory/data buses are also 32-bit. Hence, size of functional unit, datapath, internal registers, interfacing buses, memory address range are the main factors that define the 32-bit size of ARM Cortex-M4 processor.

You may refer this article for further details:

Cortex-M4 Architecture

Before discussing Cortex-M architecture, let’s first define what is architecture of a processor. Architecture of any processor is the instruction set or set of rules that defines the functionality of the microprocessor such as:

- Instruction loading

- Instruction decoding

- how it loads and stores data/instructions

- How processor access memory

There are two commonly used computer architectures i.e. Von-Numan and Harvard. Cortex-M microcontrollers are based on Harvard architecture that means they have separate instructions and data buses to access memory. That means the ARM Cortex-M processor can access both data and instructions at the same time.

Cortex-M4 Register Bank

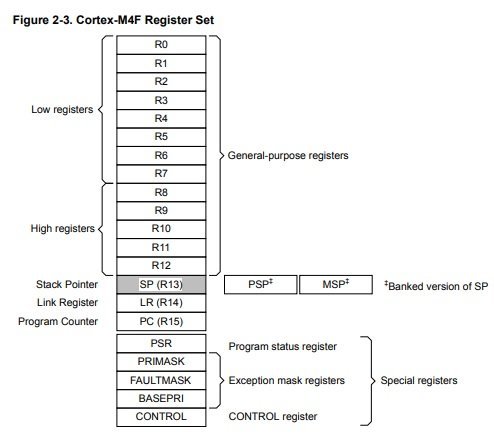

The Cortex-M microcontrollers are based on the ARMv7 processor and this processor has a set of internal registers known as a register bank. This register bank consists of 16 registers ranging from R0-R16. First 13 registers from R0-12 are general purpose registers and last three from R12-R15 are special function registers.

General Purpose Registers (GPR)

General purpose registers are divided into two groups .i.e. lower registers (R0-R7) and higher registers(R8-R12). GPR are used to store addresses and data which is currently under process.

Special Function Registers

In special function registers, R13 (SP) is a stack pointer and it holds the address of the top element of the stack. R14 is a link register LR and it is used to store the return address of the functions. R15 (PC) is a program counter and it holds the address of the next instruction to be executed. Program counter value automatically increases by 4 after every instruction execution so that it points to the next instruction address.

Special Registers

Other than register bank, the processor also has special registers that contain the program status such as operational status, system interrupts. These status registers are:

- PSR ( Program status register)

- PRIMASK

- FAULTMASK

- BASEPRI

- CONTROL

Load Store Architecture

ARM Cortex-M4 is based on load store architecture. In a load store architecture, whenever a processor wants to perform operation on data which is stored inside memory, the processor first loads this data from memory to one of the internal registers of the processor. After processing, data will be written back to memory only if it is required.

ARM Cortex-M4 instruction Set Architecture

ARM Cortex-M4 microcontrollers are based on ARMv7 architecture. Hence, Cortex-M4 MCUs support thumb-2 instruction set architecture. Thumb-2 instructions support a mixture of 16-bit and 32-bit instructions.

The original architecture of ARM is an ARM instruction set architecture. ARM ISA is 32-bit long and provides efficient performance. But its major drawback is the low code density. Therefore, in order to improve code density, ARM provided a thumbs instruction set such as thumb-1 and thumb-2. Thumb-2 ISA contains a mixture of both 16-bit and 32-bit instructions to get the performance of original ARM 32 ISA and better code density with 16-bit instructions.

Cortex-M4 Main Components

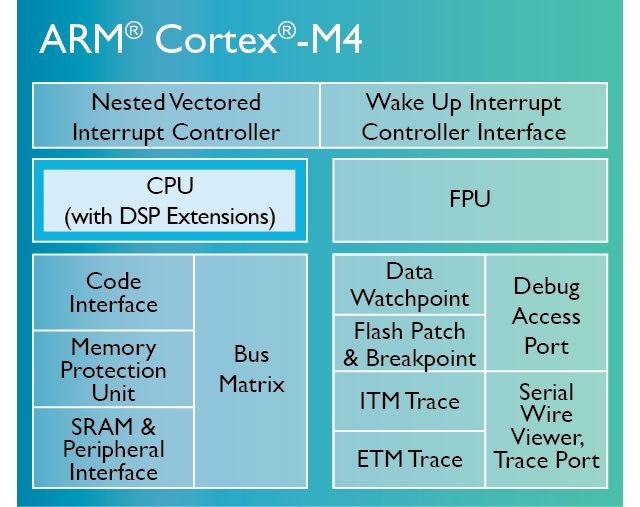

ARM Cortex-M4 based consists of the following main building blocks as mentioned below:

- Processor core

- NVIC (Nested Vector Interrupt Controller)

- Debug system

- Bus system and bus matrix

- Memory

- Peripheral

A nested vectored interrupt controller is integrated inside the microcontroller chip. The main responsibility of NVIC is to handle interrupts, prioritize interrupts, and minimize interrupt latency. ARM Cortex-M4 microcontroller supports 240 system and peripheral interrupts and NVIC performs interrupts management with the help of an interrupt vector table. You can read this article on NVIC:

The processors developed on the Cortex-M profile are typically based on a 32-bit Reduced Instruction Set Computer (RISC) architecture.

Interrupt Handling in Cortex-M4

Interrupt handling is a crucial feature in the ARM Cortex-M4 architecture, enabling the microcontroller to respond quickly to external and internal events. The Cortex-M4 includes a sophisticated interrupt handling system that allows for efficient and predictable responses to interrupts, ensuring real-time performance.

Nested Vectored Interrupt Controller (NVIC)

The Nested Vectored Interrupt Controller (NVIC) is an integral part of the Cortex-M4 processor. It supports nested interrupts, where higher-priority interrupts can preempt lower-priority ones. The NVIC is tightly integrated with the Cortex-M4 core, providing low-latency interrupt handling. It supports up to 240 external interrupt inputs, with configurable priority levels, and allows developers to enable, disable, and prioritize interrupts via a set of dedicated registers.

Interrupt Prioritization and Preemption

The Cortex-M4’s NVIC supports a flexible interrupt prioritization scheme. Interrupts can be assigned different priority levels, allowing critical tasks to preempt less critical ones. The prioritization system uses a combination of group priority and sub-priority, enabling fine-grained control over which interrupts can preempt others. This feature is essential for real-time applications, where certain tasks must be executed with minimal delay.

Interrupt Latency and Efficiency

The Cortex-M4 architecture is designed for low interrupt latency, ensuring that interrupts are serviced quickly. The NVIC and core are optimized to minimize the time it takes to respond to an interrupt, from the moment it is triggered to the start of the ISR (Interrupt Service Routine). Key factors contributing to this efficiency include automatic context saving/restoring of registers, vector table support for direct branching to ISRs, and the ability to tail-chain interrupts (where the end of one ISR directly leads into another without the overhead of returning to the main code). These features collectively enhance the responsiveness of the Cortex-M4 in real-time systems.

Cortex-M4 Security Features

Security is a vital aspect of modern microcontroller applications, particularly in fields such as IoT, automotive, and industrial control systems. The ARM Cortex-M4 provides several security features designed to protect the integrity of the system and the confidentiality of data. These features help safeguard against unauthorized access, tampering, and other security threats.

TrustZone for ARMv8-M (if applicable)

TrustZone technology, available in ARMv8-M architecture, introduces a hardware-enforced security model that divides the system into Secure and Non-Secure worlds. Although the Cortex-M4 is based on the ARMv7-M architecture and does not inherently include TrustZone, developers migrating to ARMv8-M devices can benefit from this feature. TrustZone allows sensitive code and data to be isolated in the Secure world, reducing the risk of compromise. This separation ensures that even if the Non-Secure world is compromised, the Secure world remains protected, maintaining the integrity of critical operations.

Secure Boot and Firmware Protection

Secure boot is a crucial feature for ensuring that only authenticated and trusted firmware is executed on the device. The Cortex-M4 supports secure boot mechanisms where the firmware is digitally signed, and its integrity is verified before execution. This process prevents unauthorized or malicious code from running on the microcontroller. Additionally, firmware protection features can include secure update processes, where new firmware versions are validated before being installed, ensuring the system remains secure throughout its lifecycle.

Cryptographic Hardware Accelerators

The Cortex-M4 can be equipped with cryptographic hardware accelerators, which provide hardware-based support for encryption, decryption, and other cryptographic operations. These accelerators significantly enhance the performance of security-related tasks, such as secure communication (e.g., SSL/TLS), data encryption, and authentication, without burdening the main processor. By offloading these tasks to dedicated hardware, the system not only improves efficiency but also reduces the risk of side-channel attacks, which are more prevalent when cryptographic algorithms are executed in software.

These security features collectively make the ARM Cortex-M4 a robust choice for applications where security is a top priority, ensuring that systems can protect sensitive data and maintain integrity even in the face of potential threats.

Difference Between Cortex-M0, Cortex-M0, Cortex-M1, Cortex-M3 and Cortex-M4

Cortex-M is also divided into further categories Cortex-M0, Cortex-M1, Cortex-M3, and Cortex-M4. Where the first 2 falls under the ARMv6 family and Cortex-M3 and Cortex-M4 lies under the ARMv7 family. The relationship between Cortex-M3 and Cortex-M4 is the addition of DSP (Digital Signal Processing) in Cortex-M4. There’s another profile named Cortex-M4F which differs from Cortex-M4 by only a single unit name as FPU (Floating Point Unit).

The architecture of Cortex-M3, Cortex-M4 and Cortex-M4F are all the same and the only difference is as discussed above. On the other extreme we can say that Cortex-M4 is basically a cortex-M3 profile with the integration of a DSP unit in it. The instruction set architecture used in cortex-M4 is Thumb-2 which is a mixture of 32 bit ARM instruction set architecture and 16 bit Thumb instruction set architecture. However, cortex-M4 adds a range of SIMD (single instruction multiple data) instructions to optimize the use and functioning of digital signal processing.

ARM Cortex-M Microcontrollers Applications

Application of cortex-M4 mainly lies in the areas where we need intense digital signal processing or we want to do math related operating in floating point format. Cortex-M4 and Cortex-M4F can do these operations more efficiently and fast compared to Cortex-M3. However, if you are using Cortex-M4 for applications which do not need DSP or FPU than using cortex-M4 instead of Cortex-M3 will give you no better results as the architecture of both of them are same. Below is the list of applications Cortex-M4 supports, to name a few.

- Gaming equipment.

- Motion control.

- Transportation.

- Medical instruments.

If you want to start learning ARM Cortex-M microcontrollers programming, you can read these getting started guides:

- Bare Metal Embedded Systems Build Process

- Microcontroller Booting Process

- What is Microcontrollers startup file

- Microcontroller Memory Organization and Types

- Bare Metal Embedded Systems Linker Script File

- How to use GPIO pins of TM4C123G Tiva launchPad

- Use Push Button to Control LED with TM4C123

- UART Communication TM4C123 Tiva C

- Bare-metal and RTOS Based Embedded Systems