In this article, we will see the main differences between RISC and CISC architecture. At the start, will see an introduction of RISC architecture. How its works. After that, we will go through a brief introduction of CISC architecture and its working. In conclusion, we will summarize the differences of RISC and CISC.

Basics of Computer Architecture

Almost all modern CPU has different sorts of architecture. It utilizes the capacity to work from “Instruction Set Architecture” . There are two types of this architectural design. First one is RISC (Reduced instruction set computing). The second one is CISC (Complex instruction set computing). However, both differ in various ways. RISC is a design of Central Processing Unit that has the basis of basic instruction set. It gives good performance along with a microprocessor system. In short, it has the ability to execute the commands with the help of some microprocessor cycles per command.

On the other hand, CISC has the ability to execute comlplex instructions. In other words, it can peform a large number operation with a single instruction. Furthermore, it has various modes of addressing modes to access memory. It depends on the design of the CPU where a single instruction works a lot of low-level acts. For example, loading from memory, storage into memory and an arithmetic calculation. CISC is the hardware part of the Intel and RISC is Apple hardware.

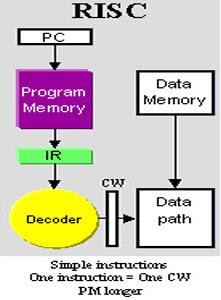

RISC Architecture Basics

The word RISC stands for ‘Reduced Instruction Set Computer’. It is such a design of the CPU that follows simple instructions and is really speedy. Basically, it is a subset of a number of instructions. In simple words, each command performs a really simple and small jobs. In such a computer, the set of instructions is simple and easy to implement. Therefore, it becomes easy to implement such commands that are really complex and difficult to execute as single instructions. Every instruction is of almost the same length. In short, it divides complex instructions into simple instructions using Piplelining. Pipelining is a multi stage process to execute instructions. Normally,it can execute a single instruction in one machine cycle.

Pipelining in RISC

This method is a pipelining which is mainly increase the speed of the RISC machines. It is a very crucial technique. Reduced Instruction Set Computer is a Architecture which is designed in such a way that it carries out only a few commands in parallel simultaneously. Due to the small size if the instructions, the chips used in this sort of architecture need a very few number of transistors. In RISC very less decoding is required. Plus, the data types in the hardware are also less. The general purpose register is the same one for all. The instruction set is uniform. And the addressing nodes are really simple. Finally when a job is being performed, RISC saves the number of cycles in which it is being executed by eliminating the unnecessary part of the code.

Characteristic of RISC Architecture

There are a lot of characteristics related to the RISC architecture, some of them are as follows:

- Simple set of instructions which are easy to decode and implement.

- The size of one instruction comes under the size of a single word.

- Only one clock cycle is required to execute a single instruction, so it is a fast process.

- The quantity of general purpose register is greater.

- The addressing modes are quite simple.

- The variable data types are very less.

- Its main idea is to achieve pipelining.

Example – Let’s suppose we are to perform addition operation on two 8-bit numbers:

The load command will be used to load the data in the registers and then the addition operator will be used on them and the result will be stored in the location of the output.

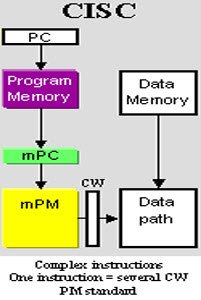

CISC Architecture Introductin

The word CISC is abbreviated as ‘’Complex Instruction Set Computer’’. It is such a design of the CPU that executes a job using only a single command. The command contains multi-step operations that program want to execute. Moreover, CISC machines have relatively smaller programs.

Whereas, the number of compound instruction size is huge. Therefore, it requires a lot of time in execution. In this type of architecture, each instruction set is very well protected in various steps. This means that there are extra three hundred instructions related to each set of instruction. Due to this, the instructions take time in their execution. Their time may vary from two to ten machine cycles, depending on the size of the instruction set. Furthermore, CISC architecture doesn’t implement pipelining normally as it is hard to.

Main Features of CISC

If we see from the prospective of compilers, CISC machines are good for them. Because the range of innovative instructions are easily obtained in a single instruction set. They execute the compound instructions in only a single and complex set of instructions. CISC is able to get processes at low-level. Hence, it is easier this way to have addressing nodes that are huge and a lot of different data types in machine hardware.

Despite of all this CISC works less efficiently than the way RISC works. This is mainly because CISC is unable to remove the portion of the code that is not required and so a lot of cycles are wasted by them when the instruction set is executed. Plus, their microprocessor chips are very difficult to manufacture and program. They are really complex.

Characteristic of CISC

There are a lot of characteristics related to the CISC architecture, some of them are as follows:

- The instruction set is complex. Hence. is its decoding.

- Instructions are normally large due to their complexity. Instructions are normally bigger than one word size.

- Usually, the compound instructions take greater time than a single clock cycle in their execution.

- The number of general purpose registers are less. Because this, it performs most operations in the memory itself.

- The addressing modes are normally complex.

- The data types are numerous.

Example – Let’s suppose we are to perform addition operation on two 8-bit numbers:

Only one instruction is used for the execution of this operation. The ADD operation will simply perform the required task. All the tasks will be done by this single command.

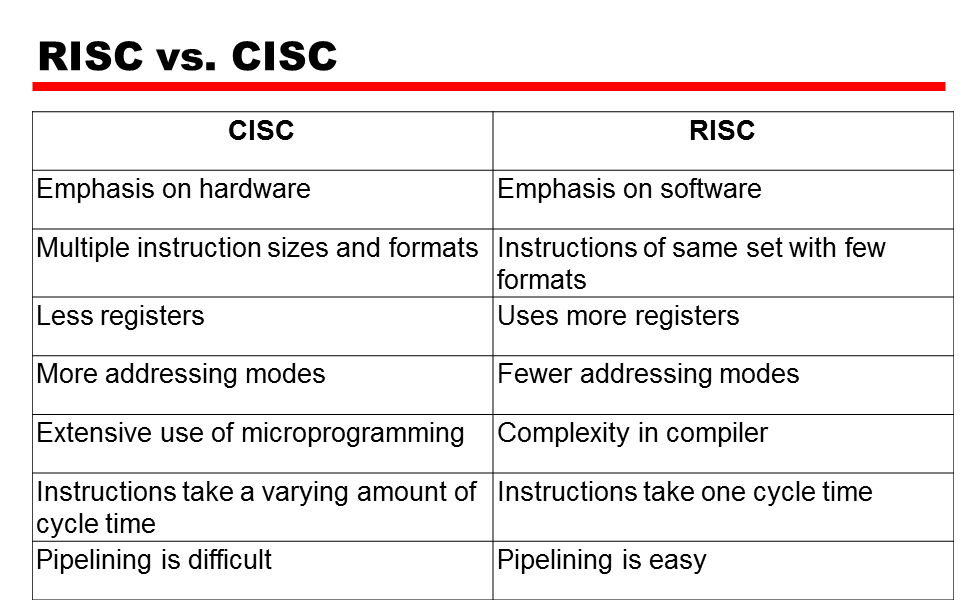

RISC vs CISC

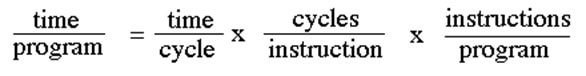

This very equation is normally used to check the performance of any computer:

This formula clearly tells that the performance of a RISC based architecture is way better than the one operating using CISC architecture. CISC and RISC are two entirely different types of computer architectures. Some of their differences are as follows:

Difference between RISC and CISC Comparison Chart

| CISC | RISC |

|---|---|

| Memory unit is present to implement the instructions | There is no memory unit and registers store data |

| It is microprogramming unit | It has a complex design of compiler |

| Its compiler design is easy | Compiler design is complex |

| Its calculations are slower yet precise | Perform mathematical calculations faster |

| Their decoding is difficult | Decoding of its instructions is easier |

| Instructions are complex so it takes time in execution | It is faster as its instructions are simple |

| External memory mandatory requirement | No external memory requirment |

| Pipelining is difficult to implement | Pipelining is easy to implement |

| Their processors often stall | There is no stalling normally |

| Code expansion is easier | The expansion of code can be an issue |

| Utilize more disk space | Consumes less disk space |

| Its examples include: include VAX, PDP-11, Motorola 68k and your desktop PCs | Its examples include: DEC Alpha, ARC, AMD 29k, Atmel AVR, Intel i860, Blackfin, i960, Motorola 88000, MIPS, PA-RISC, Power, SPARC, SuperH, and ARM |