In this tutorial, we will discuss DMA which stands for direct memory access. Firstly, we will see why we need to use DMA and what are the advantages of using DMA in modern computers and microcontrollers.

What do We need to use DMA?

The processor of a computer performs a lot of functions including data transfer between the external devices and main memory. From initializing the data transfer to storing it at the destination in the main memory, all the processing is controlled by the CPU. As the CPU is initiating, it may be the case that the processor would not be aware of the external I/O device which is ready for data transfer that may lead to data loss.

Another issue is the synchronization of microprocessors to the external I/O peripheral. In this case, the device sends an interrupt to the processor whenever it is ready but the processor requires some time to switch itself from the main program to the subroutine. But if the asynchronous I/O device is fast and generates large bulks of data it cannot wait for the delay which also leads to data loss yet again. So, to cater to this problem and maintain the efficiency of the system, a method called DMA is introduced that allows the external peripheral to access the memory directly with minimum intervention of the processor. This is implemented with the help of a controller known as DMAC that serves to be the master of the bus to control the communication at that particular time.

DMA Introduction

Direct Memory Address typically known as DMA is a data transfer technique in which I/O devices communicate directly with the memory without passing through the Central Processing Unit. In this hardware mechanism, a DMA controller substitutes the CPU unit and is responsible for accessing the input-output devices and memory for transferring data. A DMA controller is dedicated hardware that performs read and write operations directly without the involvement of the CPU and saves time that involves opcode fetching, decoding, incrementing, and source/destination test addresses that otherwise, central processing units should do. This leads to high data transfer rates between the peripherals and the memory and communicates large blocks of data speedily.

How Data transfer happen in DMA?

The data transfer is initiated by the start address, the number of words to be transferred in a block, and the direction of transferring data. The DMA controller performs the requested function as soon it receives the information. When the entire block of data is transferred, an interrupt signal is sent by the controller to inform the microprocessor that the requested operation has been completed.

For I/O operations which include the DMA, the program that has requested the data transfer is put into a suspended state by the operating system and starts to execute another program. At completion, an interrupt is raised by the DMA to tell the processor. As a result, the operating system releases the program from the blocked state back into the runnable state so that the CPU could return to the request program and continue with its further execution. During DMA transfer, the DMA controller is the master and must be synchronized with the concerned peripheral.

DMA Interface

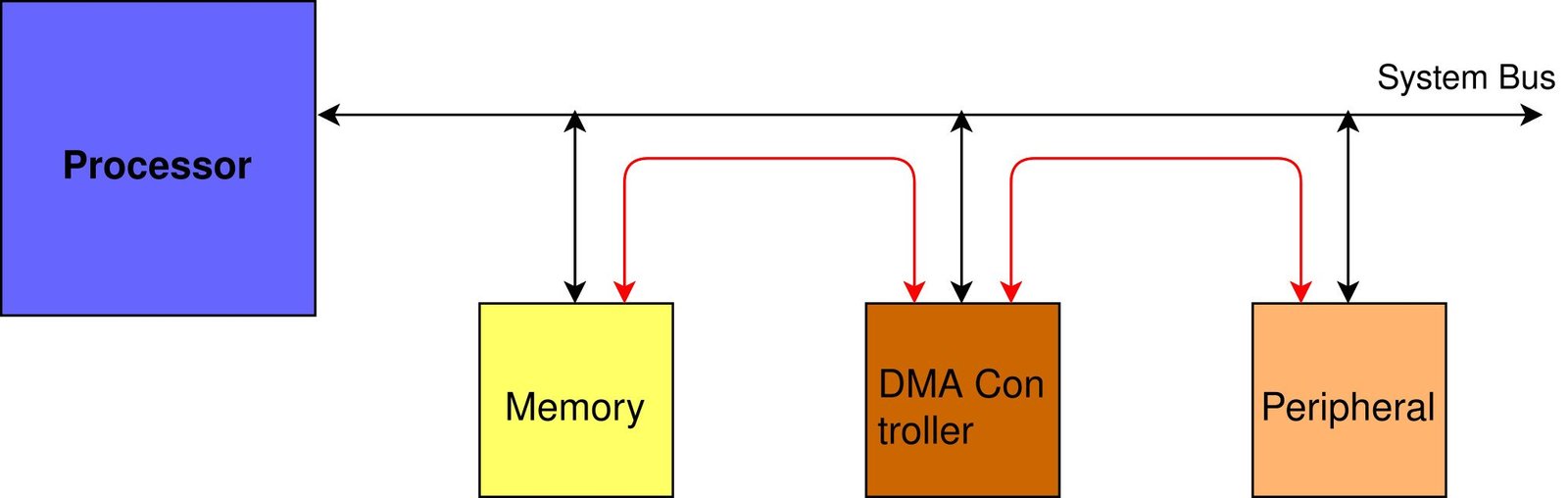

A DMA is a protocol between the external devices and the system bus. It consists of DMAC, Disk Controllers, and memory. DMAC is connected to a fast system bus which is the only medium of transfer. The Disk controllers authorize the disks and have DMA potential and can perform independent functions like the DMAC. They are also known as channels that can perform DMA data transfers according to their programming.

DMAC Controller Registers

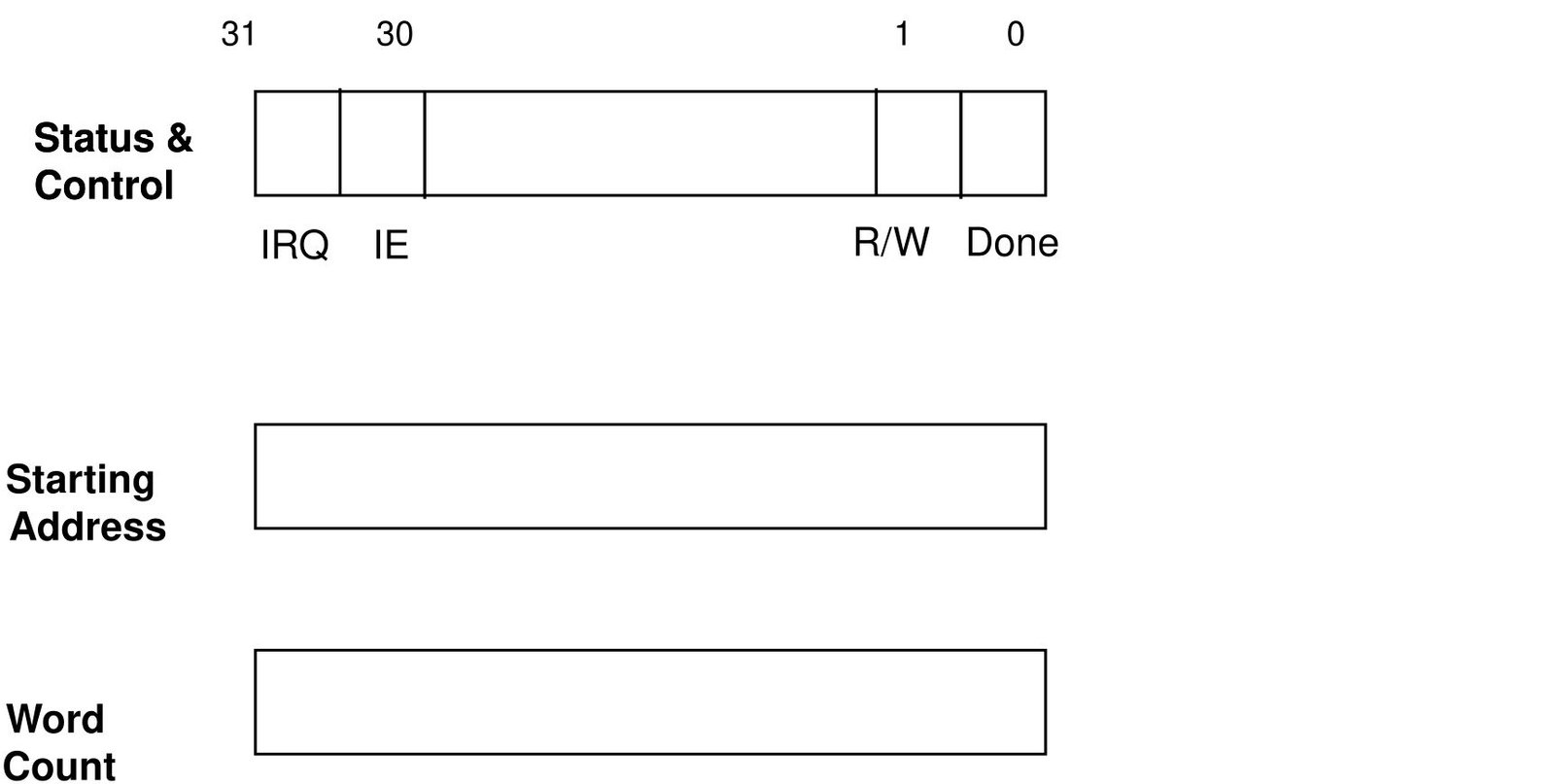

It has registers for the purpose of storing the addresses, word count, and control signals. The processor accesses controller registers to start the data transfer operations. There are two registers i.e address register and word count register to store memory address where the data is going to be stored and word count respectively and a control register to keep the status and control flags. Along with that, there is a Read/Write bit that determines the direction of data communication.

When it is instructed by the program to read i.e R/W is 1, data is transferred from the memory to the I/O device and when it is 0, it writes data from the peripheral to the main memory. When the chunk of the data is entirely transferred, DMA is ready to take in further commands. This is represented by setting the Done flag to 1. After that IE flag is raised by the DMA that enables an interrupt for the processor and also IRQ bit goes to 1 when DMA has requested an interrupt.

DMA Controller Programming Modes

Normally there are more than one general-purpose external devices connected to the bus. They make requests and are always preferred over the CPU requests. Further, out of these DMA peripherals, the faster ones are at top priority. So, the way a DMAC is programmed and caters to this situation is important. It determines the number of times it can transfer data, how many memory allocations it can access, and what type of transfer mode the DMA controller is using. On this basis, DMA Controller has three programming modes i.e. Burst mode, Cycle Stealing mode, and Transparent mode.

Burst mode

In this mode, the DMA acquires a system bus from the CPU to perform data transfer. This is the fastest mode as data is being communicated continuously. The DMAC is given priority over the CPU to execute the operation without any interruption. The processor has to wait till the DMAC finishes its work. For example, if there is a network protocol, the data block is read from the main memory and is stored in an internal buffer temporarily. It is then transferred over the network at a speed suitable to the memory and the system bus through this mode.

Cycle Stealing mode

In the cycle stealing mode, the microprocessor is controlling the computer bus but DMAC tends to steal execution cycles from the processor. In this mode, the DMAC requests the processor for bus control for one cycle and stalls the CPU. It transfers one byte and then gives back the control to the processor. In this way, the CPU does not need to wait for a long time.

Transparent mode

The mode in which the DMA controller operates and has the bus control only when the processor is not performing bus-related functions is called transparent mode. It means that the DMA can transfer data only when the system bus is idle and does not interfere with the processor executing other instructions. It is also known as a hidden mode. This is considered to be a slow yet efficient mode of direct memory access.

DMA Concept of Bus Arbitration

We know that there is only one master that can acquire the bus at a particular timestamp otherwise it can cause problems. But the processor and several DMA devices may need to use the bus at the same time to access the main memory. So to resolve this dispute and organize the activities of the DMA devices that are frequently requesting to transfer data, a procedure known as arbitration is implemented on the computer bus.

Bus Arbitration

In the bus arbitration process, a DMA device initially controls the bus and becomes the current bus master. It then transfers its data block and ultimately leaves it to pass its control onto the other DMA device. In this way, the mastership is passed and a new master is selected. Keeping the needs of the peripherals in view, they take turns to become the master and access the bus on a priority basis.

Bus arbitration has two configurations i.e Centralized arbitration in which an arbiter decides which master gets to use the bus and Distributed Arbitration that allows all the external devices to participate and acquire the next mastership of the computer bus to transfer its block.

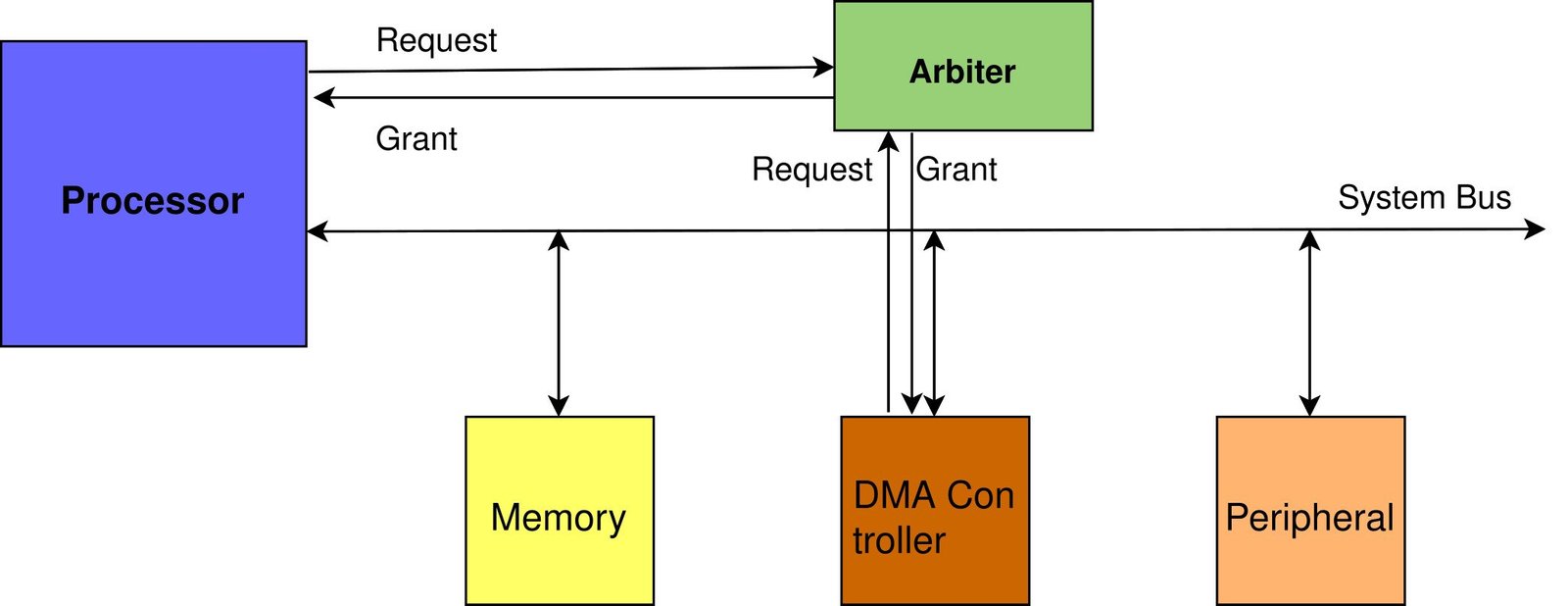

Centralized Arbitration

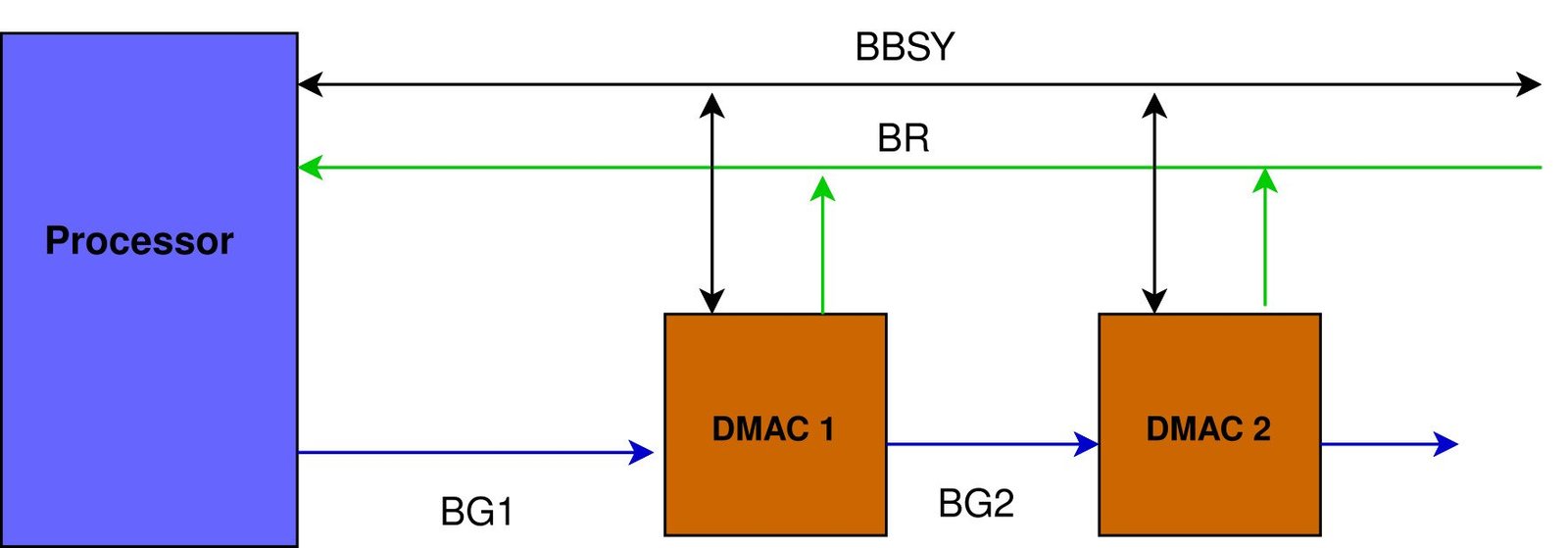

A bus arbiter can be the processor or dedicated hardware connected to the bus. Normally, the microprocessor is the bus master unless the arbiter grants the mastership to the DMA controller. Whenever DMAC wants to access the bus, it sends request signals to the arbiter and once it grants access to the DMAC, it becomes the master and starts using the bus. The DMAC sends a request by activating the Bus-request line which in return activates the bus grant signal. If more than one DMA controller is connected serially to a single bus, the signal of the bus request line is the logical OR of their requests.

In the same way, the grant signals move through all connected DMACs until it reaches the controller that made the first request. When the concerned DMAC is approached, it blocks the further propagation of the bus grant signal and activates the bus-busy line. The active bus-busy lines indicate the other devices that it is occupied at the point of the time. Now, these other devices will wait for the bus busy line to become inactive and the next preferred master will obtain the mastership of the bus.

Distributed Arbitration

In this configuration, there is no central arbiter. All peripherals have an equal right to carry out the arbitration process. For this purpose, all the DMA devices are assigned with a 4-bit long identification number. When these devices send requests to the bus, they assert the “Start Arbitration” signal, place the ID numbers onto the arbitration lines and compare the bits. The ID number generated through the arbitrary lines determines the master at that time. The device with the highest ID number is selected and allowed to access the bus for data transmission.

DMA Advantages

- Fast Data transfer between Memory and I/O devices

- CPU and DMA can operate concurrently and provides better peformance

- More Efficient use of external interrupts

- Higher data throughput

- I/O devices and peripherals communicate directly with memory