In this tutorial, we will talk about the interrupt vector table. Firstly, we will define the interrupt vector table (IVT). Secondly, we will see the role of IVT for interrupts and exceptions processing in microcontrollers or microprocessors. After that, we will see the interrupt vector table of TM4C123G ARM Cortex M4 microcontroller.

Almost all modern processors and microcontrollers support interrupts and exceptions features in order to provide event-driven tasks or threads execution possible. Unlike the polling method, event-driven tasks make use of CPU resources more efficiently. These days microcontrollers or microprocessors support hundreds of interrupts and exceptions. Each interrupt/exception has an interrupt service routine(ISR) defined somewhere in the code memory. But the question is how the processor determines where the ISR is located in code memory for the specific interrupt? The answer is simple, microcontrollers make use of interrupt vector tables to find the starting address of ISR routines.

Now lets start with the definition of IVT. This is also abbreviated as VT in literature.

What is Interrupt Vector Table ( IVT) ?

As its name suggests, it is a table that contains vectors. But what are vectors? In the physics world, the term vector means a dimension or direction. But in embedded programming, vector means memory address. Hence, a vector table is a table that contains memory addresses. But the question is, addresses of which piece of code or instructions? The answer is interrupts or exceptions. In short, the interrupt vector table contains addresses ( function pointers) of interrupt service /routines and exception handler functions.

The interrupt vector table is a table of memory addresses of interrupt/exception handler routines. In other words, it defines where the code of a particular interrupt/exception routine is located in microcontroller memory.

Interrupts and exceptions in ARM MCU

As we have discussed in the last section, the vector table contains the address of the ISR routines of all interrupts and exceptions that the microcontroller supports.

If you check the datasheet of TM4C123G ARM Cortex M4 microcontroller, it has 15 system exceptions and 138 peripheral interrupts. Peripheral interrupts are also defined as simple exceptions in literature. The main difference between system exceptions and interrupts is that system exceptions are generated by the CPU and peripheral interrupts are generated by different peripheral modules available in ARM cortex based microcontrollers.

In short, the IVT of TM4C123GH6PM microcontroller has 154 entries for all interrupts and exceptions.

But not all interrupts are available in TM4C123G microcontroller. Only 78 are available and space is reserved inside the vector table for those peripheral interrupts which are not available. These reserves interrupts might be available in other TI microcontrollers.

Where does IVT store in Microcontroller Memory?

There are types of memory in microcontrollers such as code memory or data memory. The interrupt vector table stores in flash/code memory of ARM Cortex M4 microcontrollers.

If you don’t know about types of memory or memory organization of microcontrollers, you should read this post:

Microcontroller Memory Organization and Types – Explained with Memory Segments

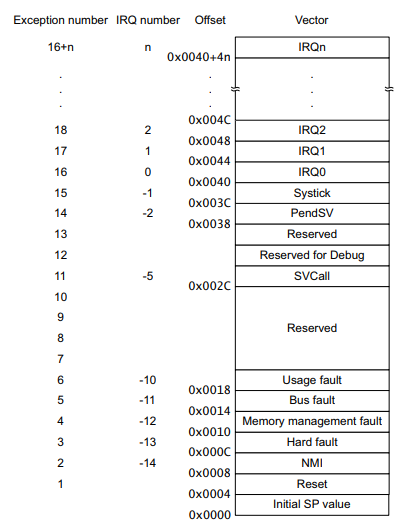

If you explore the datasheet of TM4C123GH6PM microcontroller (page 107), the interrupt vector table stores at the starting addresses of code memory ( starting from 0x0000_0000). Because TM4C123GH6PM microcontroller has 154 total exceptions (including system and simple exceptions), Therefore, the vector table contains 154 entries. The first two entries of the vector table are the initial value of the stack pointer and the address of the reset handler function. Because whenever a microcontroller resets, it performs hardware initialization steps. You can read this in-depth guide on the microcontroller booting process:

Microcontroller Booting Process – Reset Sequence

The figure below shows the interrupt vector table along with their memory addresses and memory contents. Each memory address contains the address of exception handlers. For example. the address 0x0000_003C contains the address location of the systick timer interrupt handler.

One more point to note here is the exception number. The exception number is used by ARM Cortex M CPU to index into the location of the interrupt vector table.

The vector table and interrupt service routines/exception handlers are defined inside the startup file of a microcontroller. The startup file and a linker script file define the way to store the interrupt vector table at the starting 256 locations of the microcontroller’s code memory. If you don’t know about the startup file, you should read this article:

What is Microcontrollers startup file – Understand its various Functions

Because TM4C123G MCU supports 154 exceptions and interrupts. Hence, IVT stores at first 154 words of ROM or code memory. One extra location is used to store the starting address of the main stack pointer.

Role of Interrupt Vector Table in Interrupt Processing

ARM Cortex-M CPU has two modes of operation such as thread mode and exception. In normal execution, CPU runs in thread mode. But when an interrupt occurs the CPU transfers from thread mode to exception mode. In exception mode, nested interrupt vector controller manages all interrupt and exception requests.

When an interrupt x occurs, the interrupt request will be sent to NVIC. If NVIC accepts the exception/interrupt request x, the next step of NVIC to find the starting address of the interrupt service routine or exception handler. The starting address of the respective ISR or exception handler is stored inside the interrupt vector table. Then NVIC uses exception number x to calculate the address of the exception by looking up the interrupt vector table and use the content of that memory address (which is an address of the respective exception handler) to execute the exception handler.

Program counter will be loaded with the address of the exception handler and the CPU starts to execute the exception routine.

The interrupt processing procedure of ARM cortex-M is quite lengthy. Therefore, we will post a separate article on it.

Customizing the Vector Table

In many systems, the vector table can be customized by the programmer. For instance, in embedded development using CMSIS (Cortex Microcontroller Software Interface Standard), the vector table is usually defined in a startup file or automatically handled by the development environment.

The vector table is critical for real-time systems because it enables quick and efficient response to hardware events (like timers, external signals, or internal errors) by directing the CPU to the appropriate ISR without needing complex conditional logic in the main program.

Summary

In summary, the interrupt vector table is an array of function pointers that points to the starting address of exception or interrupt handlers of a microcontroller or microprocessor. IVT usually stores at the starting addresses of flash or code memory.

Further Reading:

- Nested Vectored Interrupt Controller (NVIC) ARM Cortex-M Microcontrollers

- Accessing Memory Mapped Peripherals Registers of Microcontrollers

- Bare Metal Embedded Systems Build Process using GNU Toolchain

- Bare Metal Embedded Systems Linker Script File

- How to use GPIO pins of TM4C123G Tiva launchPad

- Use Push Button to Control LED with TM4C123G Tiva LaunchPad

very well defined

In this article it states: “The interrupt processing procedure of ARM cortex-M is quite lengthy. Therefore, we will post a separate article on it.” Was this article created?

Thanks

Yes, you can find it here:

https://microcontrollerslab.com/interrupt-processing-arm-cortex-m-microcontrollers/

Very good description of interrupt vector table.

vert similaire to the MC68000 microprocesseur IVT.

vert clear article.